#### Università degli Studi di Catania Scuola Superiore di Catania

International PhD in Nanoscience

XXV cycle

## AlGaN/GaN heterostructures for enhancement mode transistors

#### Giuseppe Greco

Coordinator of PhD

**Tutor**

Prof.ssa M.G. Grimaldi

Prof.ssa M.G. Grimaldi Dott. F. Roccaforte

Catania, 2012

To the memory of Dr. Vito Raineri, who introduced me to this wonderful adventure

#### **Contents**

| Introduction                                               | 1  |

|------------------------------------------------------------|----|

| Chapter 1: Properties of Gallium Nitride                   | 7  |

| 1.1 Historical introduction to GaN research                | 7  |

| 1.2 GaN crystal structure                                  | 12 |

| 1.3 Propierties of GaN                                     | 15 |

| 1.4 Substrates and growth techniques                       | 20 |

| Chapter 2: AlGaN/GaN heterostructures: physics and devices | 25 |

| 2.1 Al <sub>x</sub> Ga <sub>1-x</sub> N alloys             | 25 |

| 2.2 Formation of two dimensional electron gas (2DEG) in    |    |

| semiconductor heterostructures                             | 27 |

| 2.3 2DEG formation in AlGaN/GaN heterostructures           | 30 |

| 2.4 HEMT working prianciple                                | 36 |

| 2.5 Determination of the 2DEG properties from the HEMT     |    |

| characteristics                                            | 43 |

| 2.6 Open issues in current GaN HEMT technology             | 49 |

| Chapter 3: Nanoscale characterization of AlGaN/GaN         |    |

| heterostructures after near-surface processing             | 61 |

| 3.1 Fluorine-based plasma treatment of the AlGaN surface   | 61 |

| 3.2 Rapid local thermal oxidation of AlGaN/GaN             | 67 |

| Chapter 4: Au/Ni Ohmic contacts to p-GaN                   | 74 |

| 4.1 State of the art                                       | 74 |

| 4.2 Electrical characterization of Au/Ni contacts to p-GaN | 78 |

| 4.3 Structural characterization                            | 82 |

| 4.4 Nanoscale morphological and electrical analysis        | 87 |

| 4.5 Temperature dependence of R <sub>1</sub> , and o       | 91 |

| Chapter 5: AlGaN/GaN enhanchement mode HEMTs structures          |     |

|------------------------------------------------------------------|-----|

| using p-type GaN gate contact                                    | 99  |

| 5.1 Critical issue for an enhancement mode HEMT using a p-       |     |

| GaN gate                                                         | 99  |

| 5.2 Fabrication and characterization of p-GaN/AlGaN/GaN          |     |

| HEMTs                                                            | 101 |

| 5.3 Development of a "self-aligned" process for the gate of a p- |     |

| GaN/AlGaN/GaN HEMT                                               | 115 |

| 5.4 Simulations of the band diagram of p-GaN/AlGaN/GaN           |     |

| heterostructures                                                 | 119 |

| 5.5 Normally-off behavior of p-GaN/AlGaN/GaN HEMT                |     |

| structures                                                       | 126 |

|                                                                  |     |

| Chapter 6: Epitaxial nickel oxide on AlGaN/GaN heterostructures  | 134 |

| 6.1 Gate dielectrics in GaN HEMTs                                | 134 |

| 6.2 Characterization of epitaxial NiO as gate dielectric in      |     |

| AlGaN/GaN heterostructures                                       | 136 |

|                                                                  |     |

| Summary                                                          | 144 |

|                                                                  |     |

| References                                                       | 148 |

|                                                                  |     |

| Curriculum Vitae                                                 | 162 |

|                                                                  |     |

| Publications                                                     | 163 |

|                                                                  |     |

| Conferences participation                                        | 165 |

|                                                                  |     |

| Acknowledgements                                                 | 166 |

#### Introduction

In the last 30 years, *microelectronics* research activities have registered a growth with a nearly exponential rate. These continuous progresses led to the miniaturizing of devices and integrated circuits and, consequently, to an increased circuit density and complexity of the systems at lower costs. However, the critical device size for commercial products is already approaching the nanoscale dimensions. Hence, several new issues, related to the fabrication processes of new multifunctional materials and to the final device performances and reliability, are encountered. The significant development of microelectronics devices for computing technology was closely followed by that of wireless and optical communications systems.

However, the rapid expansion of computing capability related to the device miniaturization is not the unique key issue in modern electronics. In fact, today the continuous increase of electric power demand in our society has become a global concern, whose solution cannot be simply found in the device miniaturization or in the simple increase of the electric power supply. Rather, the reduction of the energy consumption through its efficient use is the main task of modern *power electronics*.

For several years Silicon (Si) has been the dominant material for semiconductor devices technology. However, the physical limits and the ultimate performances of Si, in terms of power handling, maximum operating temperature and breakdown voltage, have been already reached. In particular, due to the band gap and intrinsic carrier concentration of the material, Si devices are limited to work at a junction temperature lower than 200 °C. Hence, the material is less suitable for modern power electronics applications [1,2].

On the other hand, *wide band semiconductors* (WBG), such as silicon carbide (SiC), gallium nitride (GaN) and related alloys, exhibit superior physical properties that can better satisfy the demand of increased power, frequency and operating temperature of the devices.

SiC technology is surely the most mature among the WBG materials. First, and foremost, the size of commercial SiC wafer has been continuously increasing in the last decade and was accompanied by a reduction of the defect density (especially micropipes) [3]. Recently, 150 mm SiC wafers have been made available, thus making the processing of this material much easier even using in part the conventional Si equipments. Furthermore, the device processing technology has reached a high level of maturity and some SiC devices like Schottky diodes or MOSFETs operating in the range of 600-1200 V have already reached the market [4,5,6,7].

While SiC is undoubtedly the most mature WBG semiconductor, GaN and related alloys (like Al<sub>x</sub>Ga<sub>1-x</sub>N) still suffer from the several physical issues related to both surface and interfaces [8,9]. Furthermore, the lack of good quality (and cheap) "free standing" GaN templates make also the material growth a serious concern, since heteroepitaxy on different substrates (like Al<sub>2</sub>O<sub>3</sub>, SiC, or Si) is required. Although for long time GaN has been mainly attractive because of the optoelectronics applications, the recent improvement of the material quality of GaN-based heteroepitaxial layers provided the scientific community with considerable incentive to investigate the potentialities of this material also for applications in power electronics. As a matter of fact, some works demonstrated in the last years the possibility to fabricate Schottky diodes with a high breakdown voltage on good quality GaN material [10,11,12,13] and, lately, quasi-vertical Schottky diodes in GaN on Al<sub>2</sub>O<sub>3</sub>, with breakdown voltage of 600 V and forward current of 6 A at 1.7 V, were announced [14].

Furthermore, the continuous development of the quality of epitaxial GaN over large diameter Si-substrates (recently up to 200 mm) is resulting into significant advances also in GaN-based transistors for power switching and millimeter wave communications [15,16].

Although the low-field mobility of bulk GaN is much lower than that of other III-V materials like GaAs, GaN has a larger saturation velocity and a wide band gap, very suitable for using it as a channel material in high frequency power devices.

In this context, further contributing to the outstanding properties of GaN is the possibility to form *AlGaN/GaN heterostructures* with a large band discontinuity. In this system, a *two-dimensional electron gas (2DEG)* is formed due to the presence of both a spontaneous and piezoelectric polarization of the material. The high polarizations and resulting electric

fields in AlGaN/GaN heterostructures produce high interface charge densities even for unintentionally doped materials. In particular, the 2DEG formed is AlGaN/GaN heterostructures can have sheet carrier densities in the order of 1-3×10<sup>13</sup> cm<sup>-2</sup>, i.e., well in excess of those achievable in other III–V systems like GaAs. Moreover, the possibility to use undoped material results in a significant improvement of the electron mobility in the 2DEG, due to the reduction of Coulomb scattering with ionized impurities.

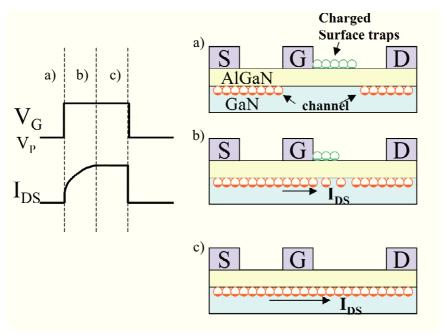

AlGaN/GaN heterostructures are particularly interesting for the fabrication of high electron mobility transistors (HEMTs), based on the presence of the 2DEG. This kind of devices were first demonstrated in GaN by Khan et al. in the 1993 [17]. In a HEMT, the sheet carrier density in the 2DEG channel is modulated by the application of a bias to a Schottky metal gate. These devices are depletion mode (normally-on), i.e., a negative bias must be applied to the gate in order to deplete the electron channel and turn the device off. Clearly, since the 2DEG is confined in the potential well arising from the band discontinuity of the two materials (AlGaN and GaN) and the conductive channel is located very close to the surface (i.e., typical thickness of the AlGaN barrier in a HEMT structure is around 20-30 nm), the physical problems affecting the operation of these devices must be investigated at a nanoscale level. Indeed, several fundamental issues related to both surfaces and interfaces in AlGaN/GaN heterostructures are today object of deep scientific investigation in order to understand the physical phenomena related to the carrier transport in these nanometric systems and, ultimately, improve the performance of HEMT devices.

As an example, one of the big problems related to GaN HEMTs is the presence of trapping centres near the surface or in the bulk of the material, that limit the maximum drain current, particularly under high frequency operation [18]. Another issue in AlGaN/GaN HEMTs is related to the high gate leakage currents at the Schottky gate, also related to the presence of electrically active near-surface defects in the thin AlGaN barrier layer. In order to overcome this problem, the use of a dielectric under the metal gate can be used to reduce the leakage current. However, the choice of the dielectric can be critical, due to the effects on the threshold voltage (the bias required to deplete the 2DEG) and, ultimately, on the device transconductance.

Surely, the most challenging aspect in the present research activity on GaN devices is the development of a reliable way to achieve an enhancement mode (*normally-off*) HEMT. In fact, enhancement mode AlGaN/GaN HEMTs would offer a simplified circuitry (eliminating the negative power supply), in combination with favourable operating conditions for device safety.

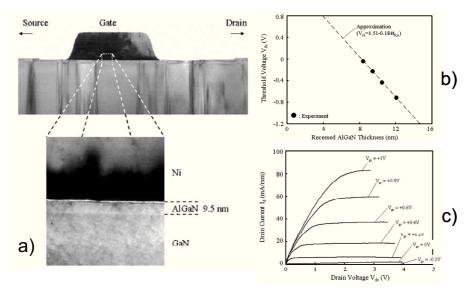

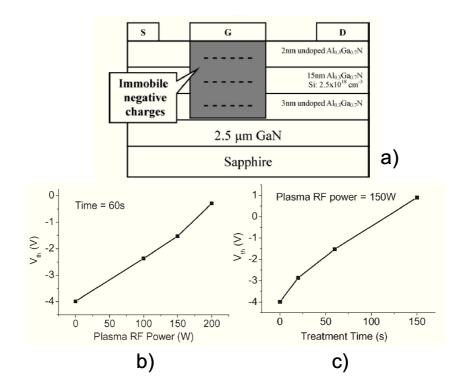

Several solutions to achieve a positive threshold voltage have been proposed, mostly involved modification of the first nanometers of the AlGaN barrier layer, like the use of a recessed gate approach, the introduction of fluorine atoms by plasma treatments, or the use of oxidation process of the near-surface. An interesting approach is the use of a p-GaN gate onto a conventional AlGaN/GaN heterostructures, rising the conduction band of the heterostructure in order to deplete the 2DEG. As a matter of fact, one company has already started to commercialize devices fabricated with such kind of approach [19].

Some of the above mentioned critical issues related to the development of enhancement mode AlGaN/GaN HEMTs with a p-GaN gate have been addressed in this thesis. In particular, the aim of this work was to clarify the mechanisms ruling the electronic transport at relevant interfaces in AlGaN/GaN devices after surface modification processes used in normally-off technologies, e.g, plasma treatments or oxidation, deposition of metal contacts or dielectrics, etc. For this purpose, in some cases the use of nanoscale electro-structural characterization techniques allowed to better explain the macroscopic electrical behaviour of these systems.

The thesis is divided in 6 chapters.

In *chapter 1*, after an historical introduction to GaN research, the main physical properties of the material are discussed, considering both the crystal structure and the electronic properties of the material (like its band gap, its spontaneous polarization, etc.) and emphasizing the reason why GaN is a suitable material for high power and high frequency device. An brief mention to the substrates used for the growth (Al<sub>2</sub>O<sub>3</sub>, SiC and Si) and the growth techniques is also given (HVPE, MOCVD, MBE).

Chapter 2 is focused on the properties of the AlGaN/GaN heterostructures. In the first part, after a brief introduction on the  $Al_xGa_{1-x}N$  alloys, the formation of the 2DEG in semiconductor heterostructures is

explained, with special attention to the case of an AlGaN/GaN systems. In the second part, the working principle of the HEMT is discussed, defining some important parameters like the threshold voltage (that will be often used in the rest of the thesis) and describing how it is possible to characterize the 2DEG properties (carrier concentration and mobility) from the HEMT characteristics. Finally the most critical scientific open issues for AlGaN/GaN-based devices are described.

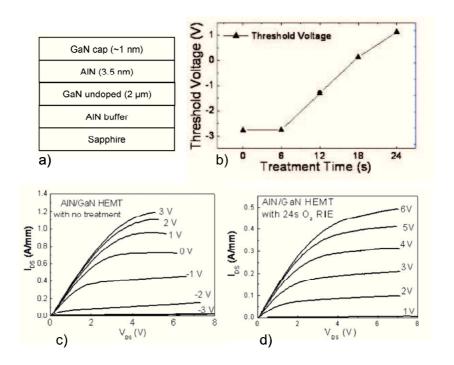

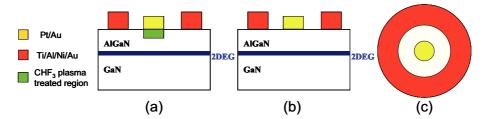

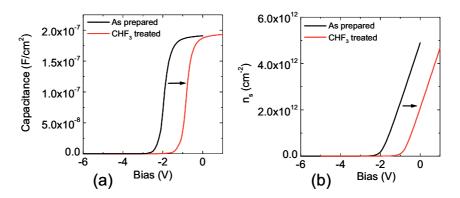

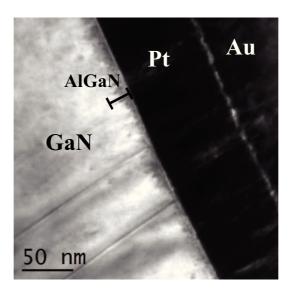

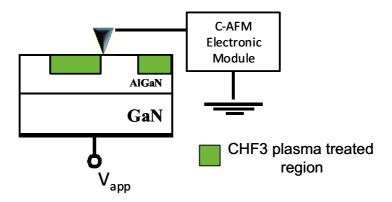

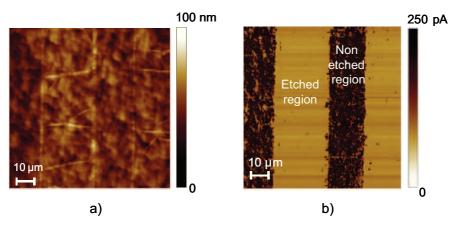

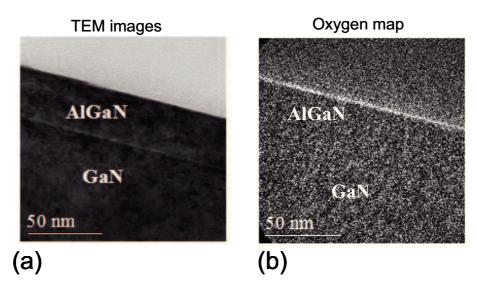

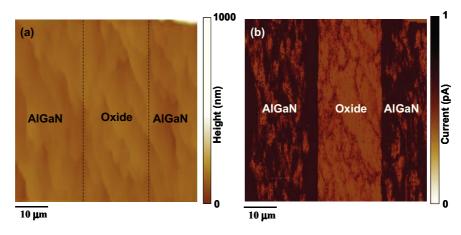

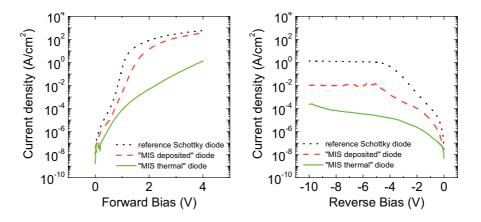

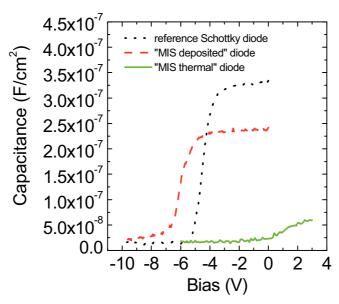

In chapter 3, a nanoscale characterization of modified AlGaN surfaces is presented in order to study possible approaches to deplete the 2DEG and obtain normally-off AlGaN/GaN HEMTs. In particular two specific different approaches have been investigated, i.e., the possibility to use a fluorine plasma treatment and the use of a local oxidation process. Both processes have the aim to modified locally the proprieties of the AlGaN barrier layer in the region below the gate electrode. To evaluate the modifications of the AlGaN properties several characterization techniques as Atomic Force Microscopy (AFM), Conductive Atomic Force Microscopy (C-AFM), Transmission Electron Microscopy (TEM) were employed in combination with macroscopic electrical measurements as Current-Voltage (I-V) and Capacitance-Voltage (C-V) measurements on fabricated test patterns. Even though a depletion of the 2DEG is possible by using these approaches, it has been concluded that several reliability concerns need to be investigated (especially in the case of the oxidation) before a practical application to devices can be envisaged.

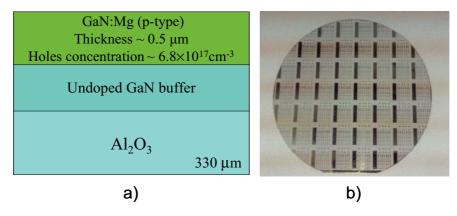

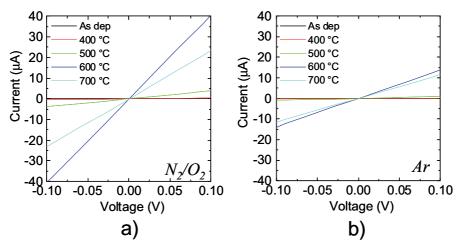

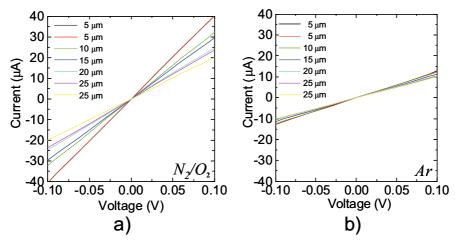

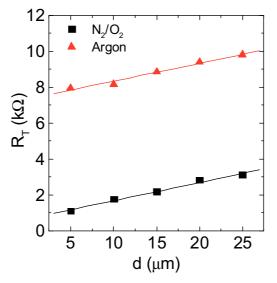

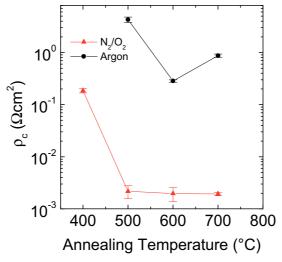

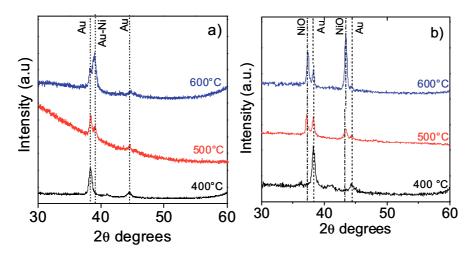

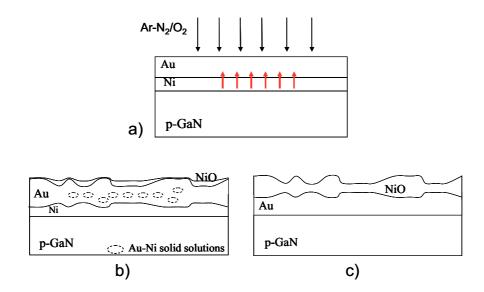

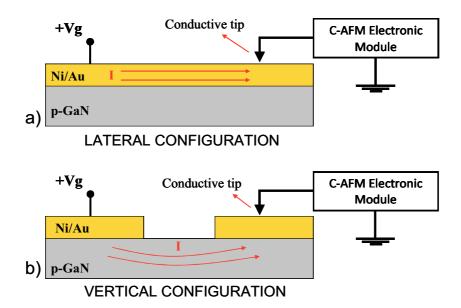

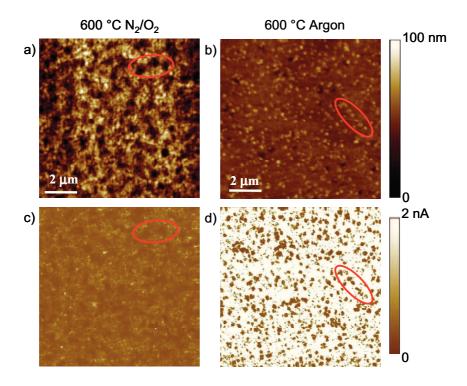

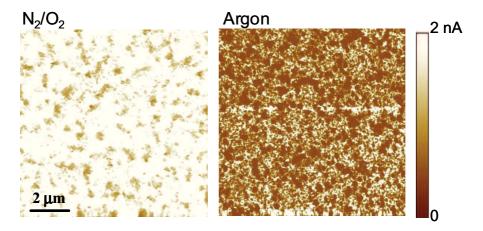

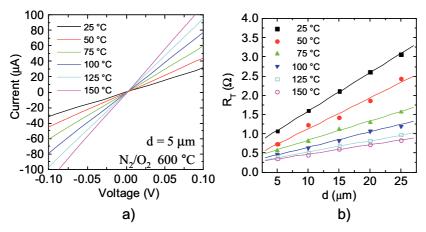

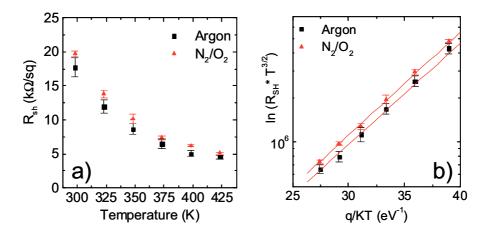

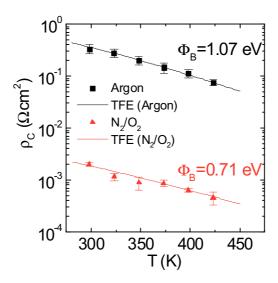

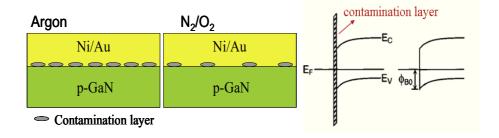

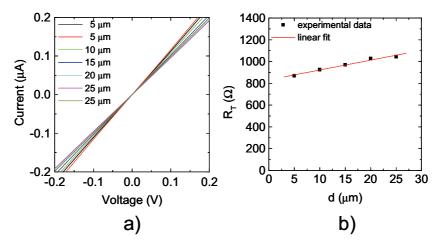

In this context, it has been pointed out that among the possible approaches for the fabrication of enhancement mode transistors using AlGaN/GaN heterostructures, the use a p-GaN gate contact seems to be the most interesting one. Hence, chapter 4 reports a detailed investigation on the formation of Ohmic contact to p-GaN, which in turn can be extremely important when using a p-GaN gate electrode. In particular, the evolution of a Au/Ni bilayer, annealed at different temperatures and in two different atmospheres (Ar or N<sub>2</sub>/O<sub>2</sub>) was considered. The experimental approach included macroscopic electrical measurements of the fabricated test patterns as Transmission Line Method (TLM) or Van der Pauw (VdP). The electrical measurements of the contacts annealed under different conditions demonstrated a reduction of the specific contact resistance in oxidizing atmosphere. Structural characterizations of the metal layer carried out by

TEM and X-Ray Diffraction (XRD), associated with nanoscale electrical measurements by C-AFM, allowed to give a possible scenario on the Ohmic contact formation mechanisms. Finally, the temperature dependence of the specific contact resistance was studied in the two cases, thus allowing the extraction of the metal/p-GaN barrier.

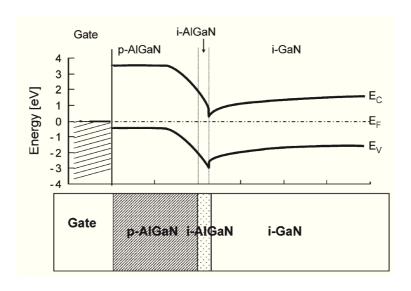

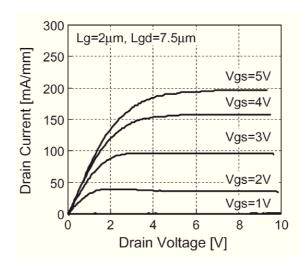

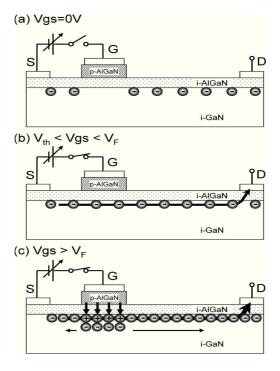

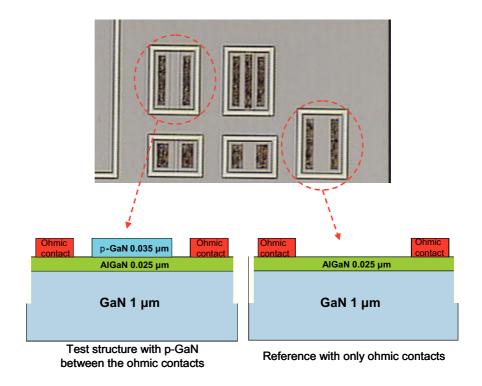

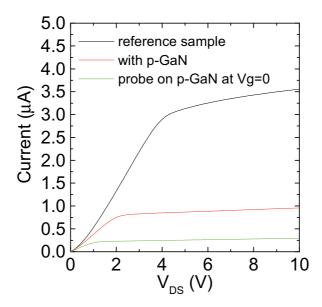

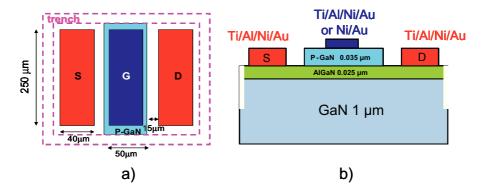

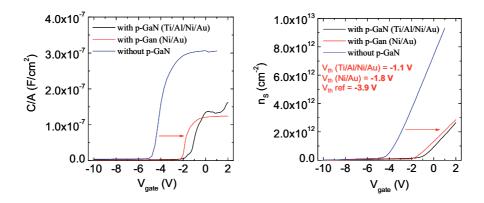

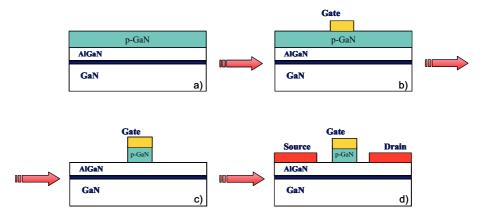

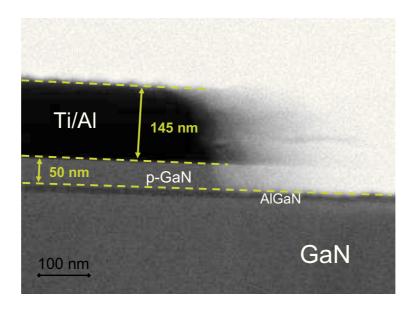

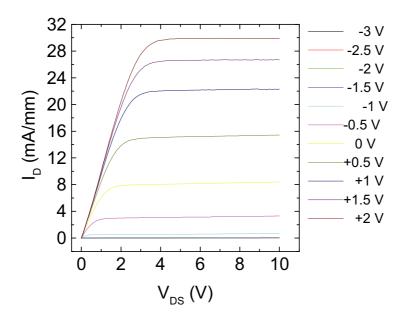

In *chapter 5*, the fabrication and characterization of AlGaN/GaN transistors with the use of a p-GaN cap layer under the gate contact is presented. Firstly, by electrical I-V measurements on simple test structures, the impact of the p-GaN layer on the 2DEG channel was demonstrated. Then, more complex p-GaN/AlGaN/GaN transistors were fabricated and characterized. The C-V measurements showed a significant positive shift of the threshold voltage ( $V_{th}$ ) with respect to devices without p-GaN gate, thus confirming the validity of our approach. Hence, basing on a simulation of the band structure, an optimized heterostructure was prepared, which led to a normally-off behaviour of the devices ( $V_{th}$  =1.4V). However, a further improvement in the material quality and processes is still needed in order to reduce the high leakage that affected the device characteristics.

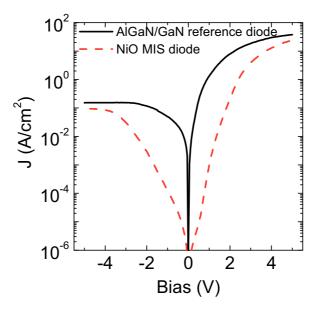

Finally, chapter 6 reports on a preliminary study on the use of nickel oxide (NiO) as a dielectric below the Schottky gate contact in AlGaN/GaN heterostructures. First, a structural and morphological investigation of the NiO layers grown by MOCVD showed continuous epitaxial film. The electrical measurements on devices allowed to extract a value of the dielectric constant for the grown NiO very close to the theoretical one, and a strong reduction of the leakge current in HEMT structures integrating such a dielectric.

The research activity presented in this work of thesis was carried out using the clean room and others characterization facilities of CNR-IMM in Catania. The activity was supported by ST Microelectronics of Catania, that provided the AlGaN/GaN heterostructures grown on Si and gave access to some processing and characterization tools. The p-GaN material and p-GaN/AlGaN/GaN heterostructures grown on Al<sub>2</sub>O<sub>3</sub> were provided by the Institute of High Pressure Physics (UNIPRESS) in Warsaw, Poland. Most of the work has been carried in the framework of the ENIAC JU Last Power project under grant agreement n° 120218.

## **Chapter 1: Properties of Gallium Nitride**

The research activity on GaN dates back to the first 1930s. However, only in the '90s the material started to attract interest for power and RF electronics, because of its superior properties such a high band gap, a high breakdown field and a high saturated electron velocity. In this chapter, after an historical introduction to GaN research, the properties of GaN will be described, introducing the figures of merit that make the material promising for power electronics applications.

## 1.1 Historical introduction to GaN research

Electronics is the basic field for information and communication technology (ICT) and for the electric power control technology required to support modern human society.

Today, the need of electric power is continuously increasing and represents a global concern. In the next years, power electronics will play an important role for the reduction of the energy consumption all over the world. In this context, it is now commonly agreed that the most suitable approach to the problem is to improve the energy efficiency of the devices that could lead to a reduction of 20% of the global energy demand [20,21].

Many discrete power electronic devices are used in the power modules for the transmission and the conversion of electric power. For these devices, a reduction of the static and dynamic losses can directly result in the overall lowering of power consumption of the system. Also the next generation of high-speed communication devices are becoming key technologies for network communication, requiring increasing operating frequency associated with portability and convenience.

Since the production of the first silicon transistor by Gordon Teal at the *Texas Instruments* [22], silicon (Si) has assumed a central role in the development of semiconductor devices. Recently however, Si technology is approaching the theoretical limits imposed by the material properties, in terms of maximum operation power, frequency and temperature.

In this general context, the research activities in modern electronics clearly hint towards new materials able to satisfy the specific need of higher operation frequency, higher output power and higher operation voltages.

The use of *wide bandgap* (WBG) materials can be considered as the best solution to meet the requirements of modern power electronics. In fact, WBG semiconductors such as silicon carbide (SiC) and gallium nitride (GaN), have been known to exhibit superior electrical characteristics compared to Si because of their inherent advantages such as high electron mobility, higher breakdown field strength and larger energy bandgap. Indeed, significant advances have been accomplished in the recent past in the growth, doping and devices processing technologies of wide bandgap materials, opening new avenues in semiconductor electronics in general, and high power electronics in particular [23].

While SiC has shown in the last two decades the most progress with respect to improved material quality and device processing, GaN is still affected by several challenging aspects, related both to specific material issues and to a non-conventional technology if compared to Si.

GaN cannot be considered as a "new" material since its history began already in the first decades of the last century. In fact, the first synthesis of GaN was achieved in 1932 by passing ammonia (NH<sub>3</sub>) over liquid gallium (Ga) at elevated temperatures. Anyway it was only in 1968 that the first large area GaN epitaxially grown on sapphire substrates by Hydride Vapor Phase Epitaxy (HVPE) was demonstrated. After that discover a rapid progress in the GaN technology was recorded, culminated in 1994 in the demonstration of the first high electron mobility transistor (HEMT) by M. Khan. From 1994 to our days, several progress has been achieved in the development of GaN technology. In 2000, Kaiser et al. were able to transfer

Silicon substrates, **HEMT** technology on growing AlGaN/GaN heterostructures by Metal Organic Chemical Vapor Deposition (MOCVD). The research of HEMTs working in normally-off operation started in 2006. Cai et al investigated the possibility to obtain normally-off AlGaN/GaN HEMTs by the introduction of fluorine ions in the AlGaN barrier layer. Over the years, several possibility has been investigated in order to reach normally-off AlGaN/GaN HEMTs. Another milestone achieved over the years in GaN technology was the use of dielectric films to insulate the gate electrode. In fact Sugiyama showed as the use of an insulating layer, not only brings benefit in order to leakage current, but also can bring several benefits in terms of threshold voltage, in the goal to achieve a normally-off devices. In addiction, in 2012, an important step in GaN technology was achieved, consisting in the growth of AlGaN/GaN heterostructures on 200 mm diameter Si(111).

*Table 1.1* summarizes chronologically the most important achievements of the scientific research on GaN.

| Year | Discovery                                                                                                                          | REF                                  |

|------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1932 | First synthesis of GaN                                                                                                             | Johnson and<br>Parsons, Crew<br>[24] |

| 1938 | Production of a powder composed by needles and platelets in order to study the crystal structure and the lattice parameters of GaN | Juza and Hahn<br>[25]                |

| 1959 | First photoluminescence measurement on small GaN crystals                                                                          | Grimmeiss <i>et al</i> [ 26]         |

| 1968 | First large area GaN epitaxially grown<br>on sapphire substrates by Hydride Vapor<br>Phase Epitaxy (HVPE)                          | Maruska and<br>Tietjen [27]          |

| 1971 | Fabrication of the first GaN light emitting diode (LED)                                                                                                  | Pankove <i>et al</i> [28,29]          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 1972 | Using magnesium (Mg) as p-type dopant was fabricated the first HVPE GaN LED, emitting at a wavelength of 430 nm (violet)                                 | Maruska <i>et al</i> [30]             |

| 1986 | Fabrication of improved GaN films grown by Metal Organic Chemical Vapor Deposition (MOCVD) on sapphire substrates                                        | Amano et al [31]                      |

| 1989 | The first p-type conducting GaN films was achieved                                                                                                       | Amano et al [32]                      |

| 1991 | Possible introduction at low temperature (450-600 °C) GaN nucleation layer to prevent defect generation                                                  | Nakamura [33]                         |

| 1992 | Mg activation by thermal annealing  First individuation of a two-dimensional electron gas (2DEG) formation at an AlGaN/GaN heterojunction grown by MOCVD | Nakamura et al. [34] Khan et al. [35] |

| 1993 | First HEMT on GaN grown by MOCVD on sapphire substrates  Theoretical prediction of piezoelectric effect in AlGaN/GaN                                     | Khan et al [17] Bykhovski et al. [36] |

| 1994 | Fabrication of the first AlGaN/GaN HEMT                                                                                                                  | Khan et al [37]                       |

| 1995 | First AlGaN/GaN heterostructure achieved by MBE on sapphire                                                                                              | Ozgur et al. [38]                     |

| 1996 | Doped channel AlGaN/GaN HEMT                                                    | Khan et al. [39]        |

|------|---------------------------------------------------------------------------------|-------------------------|

| 1997 | Quantification of piezoelectric effect                                          | Asbeck et al. [40]      |

| 1997 | AlGaN/GaN HEMT on SiC                                                           | Binari et al. [41]      |

| 1998 | First GaN MOSFET                                                                | Ren et al. [42]         |

| 1999 | First GaN BJT (Bipolar Junction Transistor)                                     | Yoshida et al. [43]     |

|      | First GaN HBT (Heterostructure Bipolar                                          | Zhang et al. [44]       |

| 2000 | Transistor)                                                                     | Kaiser et al. [45]      |

|      | AlGaN/GaN 2DEG by MOCVD on Si                                                   |                         |

| 2001 | AlGaN/GaN HEMT by MBE on Si                                                     | Semond et al. [46]      |

| 2003 | Design of GaN-based heterostructures with Back Barrier                          | Maeda et al. [47]       |

| 2004 | Reliable Ohmic contact on n-GaN technology                                      | Mohammad et al. [48]    |

|      | Normally-off AlGaN/GaN HEMT with use of fluorine plasma process                 | Cai et al. [49]         |

| 2006 | First recessed-gate structure for normally-off AlGaN/GaN HEMT                   | Saito et al. [50]       |

| 2007 | Normally-off AlGaN/GaN HEMT with<br>Thin InGaN cap layer                        | Mizutani et al.<br>[51] |

| 2009 | First normally-off AlGaN/GaN HFET with p-type GaN Gate                          | Uemoto et al. [52]      |

| 2010 | Threshold voltage control using SiN <sub>x</sub> in normally off AlGaN/GaN HFET | Sugiyama et al. [53]    |

| 2011 | AlN/GaN MOS-HEMTs with thermally                                                | Taking et al. [54]      |

|      | grown Al <sub>2</sub> O <sub>3</sub> passivation                                         |                      |

|------|------------------------------------------------------------------------------------------|----------------------|

| 2012 | AlGaN/GaN two-dimensional-electron<br>gas heterostructures on 200 mm diameter<br>Si(111) | Tripathy et al. [55] |

**Table 1.1:** Chronology of the most important achievements on GaN research.

#### 1.2 GaN crystal structure

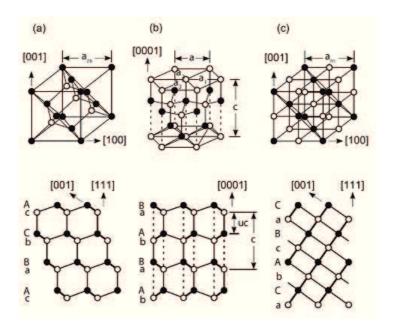

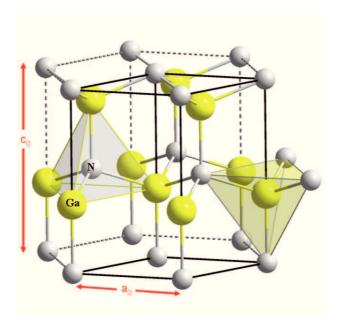

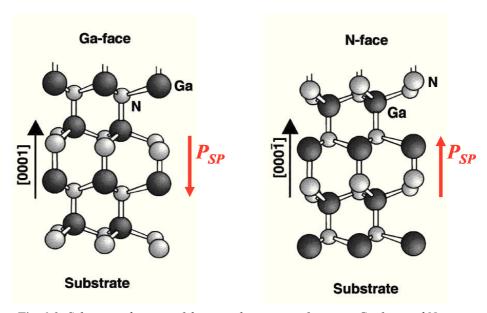

Any III-nitride material can be found in three different crystal structures as rock salt, zinc-blend or wurtzite (see Fig. 1.1). For GaN, at room temperature and atmospheric pressure, the wurtzite structure is the thermodynamically stable phase and exhibits an hexagonal unit cell with a basis of four atoms, two Nitrogen and two Gallium atoms. The unit cell of wurtzite structure is depicted in Fig. 1.2. It contains six atoms and it is characterized by two lattice constants,  $a_0$  (3.18 A) and  $c_0$  (5.18 A). The Ga and N atoms are arranged in two interpenetrating hexagonal close packed lattices (HCP), each one with one type of atoms, shifted 3/8 c<sub>0</sub> each other [56]. The covalent bonds allow that each atoms is tetrahedrally bonded to four atoms of the other type. There is also a ionic contribution of the bound due to the large difference in electronegativity of Ga and N atoms. On a wurtzite structure there is no inversion symmetry on the [0001] direction (c axis). This latter means that it is possible to distinguish two different orientation of GaN crystals, i.e., Ga-face and N-face, depending if the material is grown with Ga or N on top and corresponding to the (0001) and (0001) crystalline faces as is shown in Fig. 1.3a.

The presence of the nitrogen, because of its strong electronegativity, leads to a strong interaction between the covalent bonds. The ionicity induced by the Coulomb potential of the N atomic nucleus is responsible for the formation of a polarization effect in all the material along the [0001]

direction (see Fig. 1.3b). This effects is called *spontaneous polarization*  $P_{SP}$ , because it exists also without any introduced stress or strain. In the [111] direction of zinc-blend crystals (i.e. GaAs, GaN, AlN) there exists a similar phenomenon but with a less pronounced behaviour because the smaller ionicity of the covalent bond.

Fig. 1.1: Crystal example of (a) zinc blende, (b) wurtzite, and (c) rock salt structures.

The strength of the spontaneous polarization depends on the non-ideal (asymmetric) structure of the crystal. Not only the covalent bond in the direction parallel to  $c_0$  plays an important role, but also the other three covalent bonds of the tetrahedral structure. Their resultant polarization is aligned with  $c_0$  but in a opposite direction, compensating the polarization in the [0001] direction. For this reason in a wurtzite structure, the ratio  $c_0/a_0$  play a fundamental role for the spontaneous polarization, where the resultant  $P_{SP}$  increases with reducing the asymmetry of the crystal, i.e. decreasing the  $c_0/a_0$  ratio. For example an GaN crystal with a  $c_0/a_0$  ratio of 1.6259 will present a reduced  $P_{SP}$  (-0.029 C/m²) with respect to an AlN crystal (-0.081 C/m²) with a  $c_0/a_0$  ratio of 1.6010.

**Fig. 1.2:** The wurtzite unit cell of GaN with lattice constants  $a_0$  and  $c_0$ .

In this context, in the presence of factors that may change the ideality of the structure and the  $c_0/a_0$  ratio, as stress or strain, the total polarization will be modified.

The additional contribution to the polarization, due to the presence of strain and stress in the crystal, is the so called *piezoelectric polarization*  $P_{PE}$ . This contribution is particularly important in AlGaN/GaN heterostructures for the generation of the two dimensional electron gas and will be discussed in the next chapter.

Fig. 1.3: Schematic drawing of the crystal structure of wurtzite Ga-face and N-face GaN. The spontaneous polarization vector is also reported.

#### 1.3 Propierties of GaN

Thanks to its superior physical properties, GaN is considered an outstanding materials for opto-electronics, high power and high frequency devices. Properties like the wide band-gap, the high value of critical electric field and the saturation velocity can represent a big advantage in terms of electronic devices applications. In *Table 1.2*, some of these properties, which are relevant for electronic devices performances, are reported and compared to other semiconductors counterparts [57].

The wide band-gap of GaN (3.39 eV) is responsible for the high critical electric field (3.3 MV/cm), which is one order of magnitude higher than that of Si. The high critical electric field gives the possibility to sustain the application of high bias values, thus making the material suitable for high-voltage devices fabrication. A further implication of its wide band-gap is the

low intrinsic electron concentration  $n_i$ . The value of  $n_i$  in GaN at room temperature is in fact several orders of magnitude lower with respect to that of Si or GaAs, and comparable with that of SiC. This characteristic enables to increase the maximum operation temperature of the devices made of this material and have reduced leakage currents.

| Materials                                                            | Si                   | SiC                  | GaN                   | GaAs                | Diamond               |

|----------------------------------------------------------------------|----------------------|----------------------|-----------------------|---------------------|-----------------------|

| Properties                                                           | Si                   | (4-H)                | Guiv                  | Guzis               | Diamona               |

| Bandgap Energy $(E_g)$ , $eV$                                        | 1.12                 | 3.26                 | 3.39                  | 1.42                | 5.45                  |

| Electric<br>breakdown<br>field (Ec),<br>MV/cm                        | 0.3                  | 3.0                  | 3.3                   | 0.4                 | 5.6                   |

| Intrinsic electron concentration (n <sub>i</sub> ), cm <sup>-3</sup> | 1.5×10 <sup>10</sup> | 8.2×10 <sup>-9</sup> | 1.9×10 <sup>-10</sup> | 1.5×10 <sup>6</sup> | 1.6×10 <sup>-27</sup> |

| Electrons saturation velocity $(v_{sat})$ , $\times 10^7$ cm/s       | 1.0                  | 2.0                  | 2.5                   | 1.0                 | 2.7                   |

| Electron mobility $(\mu)$ , $cm^2/V \cdot s$                         | 1350                 | 700                  | 1200                  | 8500                | 1900                  |

| Thermal conductivity (k), W/cm·K                                     | 1.5                  | 3.3 - 4.5            | 1.3                   | 0.5                 | 20                    |

| Relative permittivity $(\varepsilon_r)$                              | 11.8                 | 10.1                 | 9.0                   | 13.1                | 5.5                   |

**Table 1.2:** Properties of GaN compared with other conventional and wide band-gap semiconductors at room temperature [58].

Other parameters that describe the quality of the material are the relative permittivity  $(\epsilon_r)$  and the thermal conductivity (k). The relatively high permittivity value  $(\epsilon_r)$  is a good indicator of the capacitive loading of a transistor and passive components. On the other hand, the thermal conductivity (k) describes the ease of heat conduction and, hence, the possibility to efficiently extract the dissipated power from the device. Materials with a lower thermal conductivity typically lead to a device degradation at elevated temperatures. Although III-V semiconductors typically have a moderate value of k, GaN has a thermal conductivity which is comparable to that of Si (but lower than SiC).

The amazing properties of GaN include also a high electrons saturation velocity ( $v_{sat}$ ), which in turn is important for high current and high frequency operation of devices. Compared to other wide band gap materials that show high  $v_{sat}$ , GaN can also reach an high electron mobility ( $\mu$ ) comparable with Si.

Undoubtedly, among wide band gap semiconductors, the unique feature of GaN is the possibility to make *band gap engineering* considering the related Al<sub>x</sub>Ga<sub>1-x</sub>N alloys. In particular, by varying the Al content it is possible to tailor the band gap of the material. In this way, AlGaN/GaN heterostructures can be fabricated, allowing to reach carrier mobility up to 2000 cm<sup>2</sup>/V·s in the *two dimensional electron gas (2DEG)* formed at the interface. The formation of 2DEG and the huge potentialities of AlGaN/GaN heterostructures will be described in the next chapter.

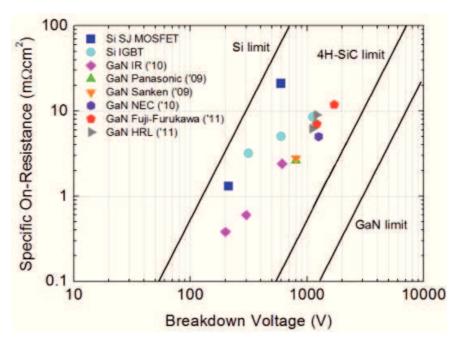

In the last decade, the most significant efforts in GaN research for electronics devices applications have been focused on the study and on the development of Schottky diodes and HEMTs. In fact, rectifyiers and switches are basic component of many electronics systems and power modules. As an example of applications, electric power converters are integrated practically in all the electronic systems to convert either DC or AC current. Their efficiency is also related to the possibility to have fast switching elements with increased power density. Typical applications of efficient power converters are the energy conversion in solar systems, wind power stations and modern electric vehicles as well as for power supplies in mobile base stations and computer systems. In all the aforementioned sectors, GaN represents today an attractive material. In fact, GaN based switches have theoretically a better figure of merit with respect to Si and

SiC. Fig. 1.4 shows the comparison between the trade-off curves of the specific on resistance  $R_{ON}$  vs breakdown voltage for Si, SiC and GaN [59].

Fig. 1.4: The Specific On-Resistance  $(R_{ON})$  versus Breakdown Voltage  $(V_{BR})$  for Si, SiC and GaN.

Some experimental data related to GaN devices taken from the literature are also reported. As can be seen, at a given operation voltage, the on-state resistance of GaN devices can, in principle, outperform the competing Si or SiC devices. Since the specific on resistance is strictly related to the power losses of the device, the use of GaN can significantly lead to a reduction of the losses and to an improvement of the efficiency of the electronic systems. However, at can be seen, the experimental data point are still far from the theoretical limits of the material.

To better compare the potential power electronic performance for different semiconductors materials, *figures of merit* (FOM) are commonly adopted. In particular, for high power and high frequency devices three important FOM are considered, Johnson (JFOM), Baliga (BFOM) and

Baliga high frequency (BHFOM).  $JFOM = (v_{sat} \cdot E_C)^2$  is an indication of the maximum capability to energize carriers by electric field,  $BFOM = \mu \cdot \varepsilon_S \cdot E_C^3$  measures the minimum conduction losses during DC operation and  $BHFOM = \mu \cdot E_C^2$  give information about the minimum conduction losses during high frequency operation. All these figures of merit for GaN are reported in  $Table\ 1.3$  and compared to Si and SiC, clearly showing that GaN is potentially a superior material for the high power and high frequency applications.

| Materials Figure of merit                    | Si                 | SiC                  | GaN                   |

|----------------------------------------------|--------------------|----------------------|-----------------------|

| $JFOM = (v_{sat} \cdot E_C)^2$               | 6×10 <sup>10</sup> | 3.6×10 <sup>13</sup> | 14.6×10 <sup>13</sup> |

| $BFOM = \mu \cdot \varepsilon_S \cdot E_C^3$ | 248                | 20.9×10 <sup>4</sup> | 79×10 <sup>4</sup>    |

| $BHFOM = \mu \cdot E_C^2$                    | 84                 | 7200                 | 20800                 |

**Table 1.3:** Figures of merit JFOM, BFOM and BHFOM for Si, SiC and GaN.

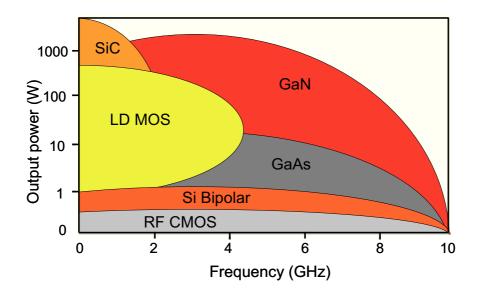

A comparison of the typical operating frequency and output power range for different semiconductor materials is shown in *Fig. 1.5*. In this case, it must be noted that with respect to SiC, GaN is more suitable for higher frequencies but in a lower output power range.

Fig. 1.5: Typical operating frequencies and output power ranges of electron devices made using a different semiconductor materials. Figure adapted from [60]

#### 1.4 Substrates and growth techniques

In spite of its outstanding material properties, the technological development of GaN has come later than in other semiconductors. The reasons of this delay were mainly related to the difficulty to have high quality free-standing GaN substrates and, consequently, the difficulty to fabricate vertical structures for power devices. In fact, for the growth of GaN other materials must be used as substrate. Since the perfect substrate does not exist, an ideal candidate must have physical and crystallographic properties, such as lattice parameters and thermal expansion coefficients, close to those of GaN, in order to avoid the formation of cracking of the film, or defects formation during the growth of the material. The lattice mismatch and the difference in *thermal expansion coefficients* (TEC) of the common substrates used for GaN growth are reported in *Table 1.4*.

Different substrates have been used for GaN growth. Sapphire (Al<sub>2</sub>O<sub>3</sub>) has been the most common substrate used for GaN heteroepitaxy for optoelectronics applications (like LEDs). Sapphire is an interesting choice because it is insulating, it can withstand the required high growth temperatures, and it is relatively cheap. Anyway the large lattice mismatch (+16%), and large thermal expansion coefficient mismatch (-25.3%) with the GaN epilayers do not make it the most convenient choice. A better substrate, in terms of lattice and thermal expansion coefficient mismatch, is the hexagonal silicon carbide (6H-SiC). The lattice mismatch for (0001)-oriented GaN films is smaller and the thermal conductivity is higher compared to the values of sapphire. In this case, however, the substrate cost represents a limiting aspect. Additionally, in spite of the minimal lattice mismatch, a high defect density (10<sup>7</sup>-10<sup>9</sup> cm<sup>-2</sup>) is still observed in GaN layers grown on SiC [61].

Silicon can be also a possible substrate for the growth of GaN layers. In the recent years, GaN materials grown on Si is attracting a huge attention thanks to the low substrate cost, the possibility of large substrate diameters and the potential integration with the well developed Si electronics technology. Despite a large lattice (+17%) and a thermal expansion coefficient (+55.5%) mismatch, GaN devices fabricated on Si substrates can have performance at the same level than those obtained on Sapphire or SiC substrates. Anyway this large mismatch is typically responsible for the formation of defects and cracks on the material. The main problem to the growth of GaN on Si substrate comes from the compressive stress generated during the growth. For this reason, to achieve a good material quality, the stress has to be minimized. Fu et al [62] showed that the residual stress is depending on the growth condition and cool-down procedure. Moreover there exists a dependence of the stress on the impurity concentrations, that lead to an increase of the tensile stress with increasing the doping concentration [63]. To relieve the tensile stress and achieve crack-free GaN heterostructures, several kind of transition layers can be used, such as low temperature AlN [64], graded AlGaN buffers [65] or AlGaN/GaN superlattices [66]. It has been seen that the dislocation density in the material strongly depends on the choice of the transition layer, and can be partially mitigated by using a high temperature AlGaN intermediate layer that acts as a dislocation filter [67]. Moreover transition layers increase also the series resistance in the GaN layer, reducing the crack density and providing a good electrical insulation from the substrates. Recently, crack-free AlGaN/GaN heterostructures grown on 200 mm diameter (111)-oriented silicon substrates has been demonstrated [16]. This results represent an important step for the full integration of GaN technology with silicon process foundries based on CMOS (Complementary Metal Oxide Semiconductor) technology. In order to obtain high quality AlGaN/GaN heterostructures on 200 mm Si substrate, thick GaN buffer layers (in the order of 2.4-2.5  $\mu$ m) were grown.

| Substrate                             | Lattice mismatch | Difference in thermal expansion coefficient (TEC) |

|---------------------------------------|------------------|---------------------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> (0001) | + 16 %           | - 25.3 %                                          |

| 6H-SiC (0001)                         | + 3.5 %          | + 33.3 %                                          |

| 3C-SiC (111)                          | + 3 %            | + 24.4 %                                          |

| Si (111)                              | - 17 %           | + 55.5 %                                          |

| AlN (0001)                            | + 2.5 %          | + 33.3 %                                          |

**Table 1.4:** Lattice mismatch and difference in thermal expansion coefficient of GaN with respect to the most common substrates

If the choice of a suitable substrate is an important issue for the development of GaN technology, not less important are the growth techniques employed to obtain a high quality material, with a low concentration of defects. The first technique used to grow epitaxial GaN layers was the Hydride Vapor Phase Epitaxy (HVPE). This technique remained the most commonly used method until the early 1980s. In this technique the gallium monochloride (GaCl) precursor is synthesized inside a reactor by the reaction of hydrochloric acid (HCl) with liquid Ga at temperatures between 750 °C and 900 °C. Then the GaCl, transported in

some proper substrates, will react with the ammonia (NH<sub>3</sub>) at 900-1100  $^{\circ}$ C forming the GaN film. Finally the exceeding substrate can be removed by system such as laser ablation. HVPE have a really high growth rate (100  $\mu$ m/hr), useful more for large area quasi substrate that have to be later completed by other epitaxial techniques as MOCVD and MBE.

Nowadays, the Metal Organic Chemical Vapor Deposition (MOCVD) has become the most used method to grow GaN, owing its superior quality as high degree of composition control and uniformity, reasonable growth rates (1-2  $\mu$ m/hr), the possibility to use high purity chemical sources and to grow abrupt junctions. MOCVD uses the reaction of trimethylgallium (TEGa) and NH<sub>3</sub> that occurs close the substrate. To obtain high quality GaN film, during the deposition the substrate must be kept at a temperature of about 1000 °C - 1100 °C, to allow a sufficient dissociation of the NH<sub>3</sub> molecule, at a pressure between 50 and 200 Torr. Moreover, another critical aspect is the control of the N/Ga molar ratio, that must be kept high in order to compensate N losses due to the high partial nitrogen pressure at the elevated growth temperatures [68].

In fact the poor nucleation of GaN on Si at high temperatures results in a reaction of nitrogen with Si and in a Ga-Si alloy formation which initiates a strong and fast etching reaction (melt back etching) destroying the substrate and the epitaxial layer [69]. The most established method to prevent the nitridation is starting the growth process with an AlN nucleation larger grown in the same reactor with a few monolayers pre-deposition of Al. [70]

The material doping can be tailored by the induction of extra precursor on the reactor, as silane (SiH4) for Si doping (n-type) or biscyclopentadienylmagnesium (Cp<sub>2</sub>Mg) for Mg doping (p-type). Anyway the control of a low doping concentration ( $N_D < 1 \times 10^{16}$  cm<sup>-2</sup>) is still a complex factor because the formation of nitrogen vacancies, which act as donors leading to n-type doping of the material. Also the oxygen impurities present during the growth process can act as donors, leading to a n-type material [71]. The p-type GaN epitaxial layer that were used in this work of thesis has been obtained by the use of Mg as dopant specie.

To improve the crystalline quality of the grown GaN, pre-treatments can be required. For example the deposition of a thin low temperature buffer layer can be an advantage. The use of this layer, generally AlN or Si, can reduce the lattice mismatch, providing a benefit in terms of defects density (dislocations, oxygen impurity, nitrogen and gallium vacancies, etc).

To reduce the defects density in the grown material, a different process called lateral epitaxial overgrowth (LEO) has been also developed [72]. It consists in the deposition of GaN on a patterned dielectric substrates (like  $SiO_2$ ) followed by the lateral expansion and coalescence of the grown material. Although this technique can lead to a significant reduction of the dislocation density (up to  $6\times10^7$  cm<sup>-2</sup>), the extremely high cost of the process (which require the employment of lithographic steps for the substrate preparation) has limited its practical application for GaN growth.

The Molecular Beam Epitaxy (MBE) is a slow (1 μm/hr) but efficient technique for GaN growth, that show comparable material quality to those grown by MOCVD. A problem is that the NH<sub>3</sub> is very stable at the low temperature (700-800 °C) used in MBE. To solve this issues reactive species of nitrogen, generated by electron cyclotron resonance (ECR) or radio frequency (RF) plasmas with low energy, are generally used [73].

In this work of thesis, mostly GaN layers grown on 150 mm Si (111) substrates, supplied by ST Microelectronic, were used. GaN has been growth by MOCVD using precursor as trimethylgallium (TEGa) and NH<sub>3</sub>. Also GaN material grown on 2 inch Al<sub>2</sub>O<sub>3</sub> wafers, supplied by the Institute of High Pressure Physics of Warsaw, has been used for the some experiments.

# Chapter 2: AlGaN/GaN heterostructures: physics and devices

One of the most interesting aspects related to GaN materials is the possibility to grow AlGaN/GaN heterostructures, in which a two dimensional electron gas (2DEG) is formed at the heterojunction. In this chapter, the physics of AlGaN/GaN heterostructures is discussed, considering the band structure and the piezoelectric polarization of the materials to explain the formation of the 2DEG. Moreover, the operation principle of HEMTs devices is described. In the last paragraph, the possible approaches to obtain normally-off HEMTs in GaN will be briefly discussed.

#### $2.1 \text{ Al}_x\text{Ga}_{1-x}\text{N} \text{ alloys}$

As pointed out in the previous chapter, GaN is characterized by the possibility to grow heterostructures based on Al<sub>x</sub>Ga<sub>1-x</sub>N alloys.

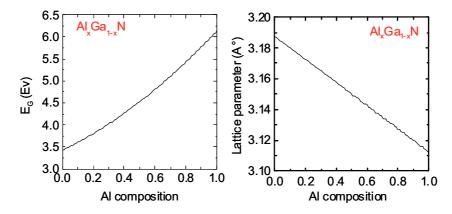

The peculiarity of  $Al_xGa_{1-x}N$  alloys is the possibility to tailor the lattice constant and the energy gap by varying the Al concentration x.

In particular, the in-plane lattice constant a of  $Al_xGa_{1-x}N$  alloys depends on the Al concentration x, and is also related to the lattice constant of GaN and AlN by the relation [74]

$$a^{AlGaN}(x) = xa^{AlN} + (1-x)a^{GaN}$$

(Eq. 2.1)

On the other hand, also the band gap of a  $Al_xGa_{1-x}N$  alloy can be expressed as a function of the Al mole fraction [75] according to

$$E_g^{AlGaN}(x) = xE_g^{AlN} + (1-x)E_g^{GaN} - x(1-x) = [x \cdot 6.13 + (1-x) \cdot 3.42 - x(1-x)] eV$$

(Eq. 2.2)

The dependence of the lattice constant and of the band gap energy on the Al mole fraction in a  $Al_xGa_{l-x}N$  are reported on Fig.~2.1a and Fig.~2.1b respectively. A schematic of the crystal structure for AlGaN/GaN heterostructure is represented in Fig.~2.2.

**Fig. 2.1:** Dependence of the band gap energy (a) and of the lattice parameter a (b) on the Al mole fraction for the  $Al_xGa_{l-x}N$ .

The big advantage of AlGaN/GaN heterostructures consists in the formation of a *two dimensional electron gas* (2DEG) at the interface, generated by the strain induced by the lattice mismatch between GaN and AlGaN. The presence of the 2DEG allows the fabrication of an innovative device called *High Electron Mobility Transistor (HEMT)* that will be discussed in the following paragraphs.

Fig. 2.2: Schematic of the structure for AlGaN/GaN heterostructure.

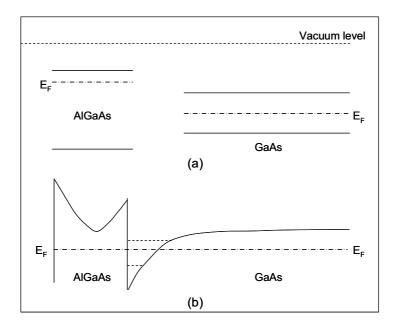

## 2.2 Formation of two dimensional electron gas (2DEG) in semiconductor heterostructures

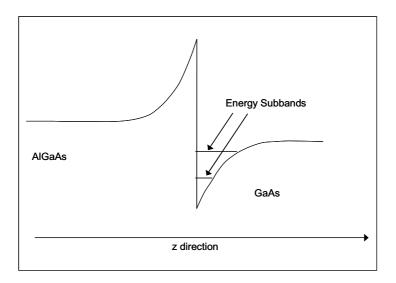

In general, when a n-type doped wide band gap semiconductor layer is brought into contact with a narrow band gap semiconductor layer, an electrons transfer will occur, accompanied by a band bending in the upper part of the narrow band gap semiconductor. In this way, a triangular well is formed, in which the transferred electrons are confined and form a two dimensional conductive channel (see *Fig. 2.3*). The electrons of the n-type doped barrier layer collected in the quantum well are commonly referred as two dimensional electron gas (2DEG), since they behave as free particles in two directions (in the plane of the interface) while their motion is quantized only in orthogonal direction. The separation of electrons from their donor atoms N<sub>D</sub> reduces the Coulomb scattering and leads to a high mobility of the electrons in the 2DEG. The possibility to have a significant increase of the

free carrier concentration within a semiconductor layer without the intentional introduction of dopant impurities is often referred as *modulation doping*.

Fig. 2.3: The energy band diagrams of the AlGaAs and GaAs layers when apart and in equilibrium (a) and the energy band diagrams after the formation of the AlGaAs/GaAs heterostructures (b).

An example of this situation can be found in the AlGaAs/GaAs heterostructures. When the two semiconductors are separated (Fig. 2.3a) the Fermi level in AlGaAs will be closer to the conduction band edge with respect to its position in the GaAs, since the AlGaAs is intentionally n-type doped. When the two semiconductors are put in contact (Fig. 2.3b), the Fermi levels will align and a transfer of electrons from the AlGaAs to the GaAs layer occurs. This effect significantly increases the electron concentration at the interface with the GaAs layer, without any introduction of ionized donor impurities. To maintain the charge neutrality of the system, the electrons flowing towards the GaAs layer leave positive ionized donor atoms behind. The spatial separation between the ionized donors atoms (located inside the AlGaAs) and the free electrons (confined inside the

triangular well at the heterointerface) significantly reduces the Coulomb scattering of the transferred electrons by the ionized impurities effects, thus leading to an increase of the electron mobility in the 2DEG.

Hence, because of the electron transfer, the conduction band edge in the GaAs layer is strongly bent near the heterostructure. Moreover a net positive charge will be present at interface, because of the positive ionized donors. Therefore, the electrons placed in the GaAs near the interface, will be attracted to the interface by the action of the positive charge. The sharp bending of the conduction band edge and the presence of the conduction band edge discontinuity forms a potential triangular quantum well within the GaAs layer. The electrons will drop in this triangular quantum well, positioning in discrete levels of energy, called *subbands*. For this reason the electrons will be free to move in all the direction parallel to the interface, because no quantization of the space occurs, while along the direction perpendicular to the interface (direction z showed in *Fig. 2.4*), they are confined by band bending in the quantum well close to the interface.

Fig. 2.4: The conduction band edge discontinuity in the n-AlGaAs and i-GaAs heterojunction, showing two energy subbands

### 2.3 2DEG formation in AlGaN/GaN heterostructures

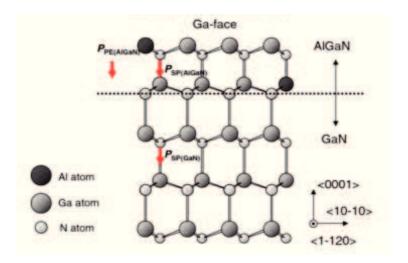

As explained in the Chapter 1, a spontaneous polarization is present in GaN. However, due to the piezoelectric nature of the material, when an AlGaN/GaN heterostructure is formed, the strain induced by the lattice mismatch generates an additional contribution to the polarization, namely, the *piezoelectric polarization*  $P_{PE}$ .

For this reason, in contrast to the conventional III-V semiconductors (like the example of AlGaAs/GaAs heterojunction described in paragraph 2.2) where a n-type doped barrier layer is necessary to provide the charges for the 2DEG formation, a different situation occurs in AlGaN/GaN systems. In this case, due to the presence of the piezoelectric polarization the formation of a high sheet charge density in the 2DEG is possible even using undoped layers. The possibility to use undoped layers in AlGaN/GaN systems (with respect to other system like n-type doped AlGaAs/GaAs heterojunction) further reduces the Coulomb scattering, leading to an enhanced electron mobility in the 2DEG.

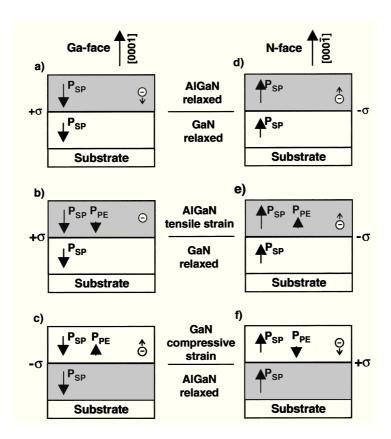

As schematically drawn in Fig. 2.5, when an AlGaN/GaN heterojunction is formed the piezoelectric and the spontaneous polarization act in the same direction, thus leading to an overall increase of the total polarization. This is the case when a tensile strain is applied to the crystal. The strength of the piezoelectric polarization  $P_{PE}$  is related to the piezoelectric coefficients  $e_{33}$  and  $e_{31}$  through the relation:

$$P_{PE} = e_{33} \cdot \varepsilon_z + e_{31} \cdot (\varepsilon_x + \varepsilon_y)$$

(Eq. 2.3)

where  $\varepsilon_z = (c - c_0)/c$  is the strain along the c-axis,  $\varepsilon_x = \varepsilon_y = (a - a_0)/a$  are the inplane strains assumed to be isotropic, and  $a_0$  and  $c_0$  are the equilibrium lattice constants. The relations between the lattice constants a and c of the hexagonal GaN is given by

$$\frac{c - c_0}{c_0} = -2\frac{C_{13}}{C_{33}} \cdot \frac{a - a_0}{a_0}$$

(Eq. 2.4)

where  $C_{13}$  and  $C_{33}$  are the elastic constants. In order to take into account the piezoelectric polarization in the direction of the c-axis, the following relation is considered:

$$P_{PE} = 2\frac{a - a_0}{a_0} \left( e_{31} - e_{33} \frac{C_{13}}{C_{33}} \right)$$

(Eq. 2.5)

*Table 2.1* report the lattice parameters, piezoelectric constants, elasticity constants, and spontaneous polarization for GaN and AlN [76][77].

| Parameter                  | AlN    | GaN    |

|----------------------------|--------|--------|

| <i>a</i> <sub>0</sub> (nm) | 0.3112 | 0.3189 |

| e31 (C/m²)                 | -0.60  | -0.49  |

| e33 (C/m²)                 | 1.46   | 0.73   |

| C <sub>13</sub> (GPa)      | 108    | 103    |

| C <sub>33</sub> (GPa)      | 373    | 405    |

| $P_{SP}(C/m^2)$            | -0.081 | -0.029 |

**Table 2.1:** Values for lattice parameters, piezoelectric constants, elasticity constants, and spontaneous polarization for GaN and AlN

Since the term  $\left(e_{31}-e_{33}\frac{C_{13}}{C_{33}}\right)$  is always negative independent of the composition of the AlGaN barrier layer, the piezoelectric polarization will be

negative for tensile strain (a >  $a_0$ ) and positive for compressive strain (a <  $a_0$ ). In the case of Ga-face heterostructures, the spontaneous polarization vector of GaN will be pointing towards the substrate (negative). For this reason the alignment between spontaneous and piezoelectric polarization will be parallel in case of tensile strain and antiparallel in case of compressive strain. On the other hand, considering the N-face, the spontaneous and piezoelectric polarization will have the opposite signs, with the vector of the spontaneous polarization pointing in the reverse direction, away from the substrate. The directions of the *spontaneous* ( $P_{SP}$ ) and *piezoelectric polarization* ( $P_{PE}$ ) are shown in *Fig. 2.5*, where also the polarization induced sheet charge density ( $\sigma$ ) is indicated.

Fig. 2.5: Spontaneous and piezoelectric polarization in Ga- and N-face strained and relaxed AlGaN/GaN heterostructures. Figure taken from Ref. [74].

Considering a gradient of polarization in space **P**, there exists a polarization-induced charge density  $\rho_P = \nabla P$  associated to this gradient. In the presence of an abrupt interface AlGaN/GaN or GaN/AlGaN (top/bottom layer) the total polarization will create *a polarization sheet charge density*  $\sigma$  defined by:

$$\sigma = [P(top) - P(bottom)] = [P_{SP}(top) + P_{PE}(top)] - [P_{SP}(bottom) + P_{PE}(bottom)]$$

(Eq. 2.6)

Hence in an AlGaN/GaN interface, with a relaxed GaN bottom layer, it is possible to estimate the amount of sheet charge density:

$$\sigma = [P_{SP} + P_{PE}]^{AlGaN} - [P_{SP} + P_{PE}]^{GaN} = \left[ P_{SP}(x) + 2 \frac{a(0) - a(x)}{a(x)} \left( e_{31}(x) - e_{33}(x) \cdot \frac{C_{13}(x)}{C_{33}(x)} \right) \right] - [P_{SP}(0)]$$

(Eq. 2.7)

where x is the Al mole fraction in the AlGaN layer. Of course, considering a GaN/AlGaN heterostructures the polarization has the opposite sign and the sheet charge density will be negative.

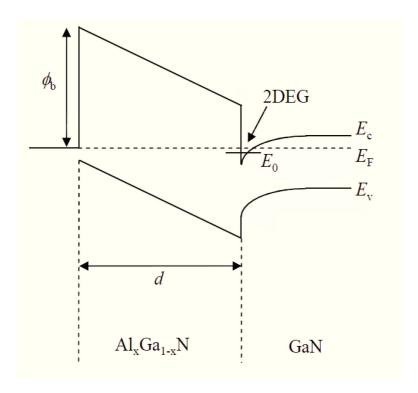

The polarization charge is due to the piezoelectric effect in strained AlGaN and to the difference in spontaneous polarization between AlGaN and GaN. Piezoelectric constants and spontaneous polarization increase moving from GaN to AlN, so the total polarization of AlGaN layer is larger than of GaN buffer layer and therefore a positive polarization charge is present at lower AlGaN/GaN interface, for Ga-face structure. Then the electrons will tend to compensate this positive charge resulting in the formation of the 2DEG in the triangular quantum well at the AlGaN/GaN interface, whose ground subband level lies below the Fermi level E<sub>F</sub>. In *Fig. 2.6* the band structure for a Ga-face undoped AlGaN/GaN heterostructure is shown. In the case of N-faced structures a negative polarization charge will be compensated by holes and these will be accumulated at the interface.

**Fig. 2.6:** Energy band diagram of a Ga-face undoped AlGaN/GaN heterostructure.

To determine the effective sheet charge density of the 2DEG, different parameters must be considered like the polarization induced bound sheet charge density at the AlGaN/GaN heterojunction  $\sigma_{int}$ , the Schottky barrier height  $\phi_B$  formed at the metal/AlGaN contact, the Fermi level at the heterojunction with respect to the GaN conduction band edge  $E_{F0}$ , the conduction band offset at the AlGaN/GaN interface  $\Delta Ec$  and the relative dielectric constant  $\varepsilon_{AlGaN}$ , the thickness  $d_{AlGaN}$ , and the Al mole fraction x of the AlGaN barrier layer. From these parameters is possible to give an expression of the sheet charge density  $n_S$  located at the AlGaN/GaN interface by the Eq. 2.6 [78]

$$n_{S}(x) = \frac{\sigma_{\text{int}}}{q} - \left[ \frac{\varepsilon_{0} \varepsilon_{AlGaN}(x)}{d_{AlGaN} q^{2}} \right] \cdot \left[ q \phi_{B}(x) + E_{F_{0}}(x) - \Delta E_{C}(x) \right]$$

(Eq. 2.8)

where q is the elementary charge and  $\varepsilon_0$  is the vacuum permittivity.

As can be seen, the sheet carrier concentration induced by the polarization sheet charge density is a function of the Al concentration x present in the AlGaN barrier layer. For an AlGaN/GaN heterojunction we can consider  $\varepsilon_{AlGaN}(x)$  and  $\phi_B(x)$  given by [79]

$$\mathcal{E}_{AIGaN}(x) = -0.5x + 9.5$$

(Eq. 2.9)

and

$$q\phi_{R}(x) = 1.3x + 0.84 \text{ eV}$$

(Eq. 2.10)

The Fermi energy is given by [80]

$$E_F(x) = E_0(x) + \frac{\pi \hbar^2}{m^*(x)} n_S(x)$$

(Eq. 2.11)

where  $m^*_{AlGaN}(x) \approx 0.22 m_e$  is the effective electron mass and  $E_0(x)$  represent the ground subband level of the 2DEG [81] [82]

$$E_0(x) = \left[ \frac{9\pi hq^2}{8\varepsilon_0 \sqrt{8m_{AlGaN}^*(x)}} \frac{n_S(x)}{\varepsilon_{AlGaN}(x)} \right]^{2/3}$$

(Eq. 2.12)

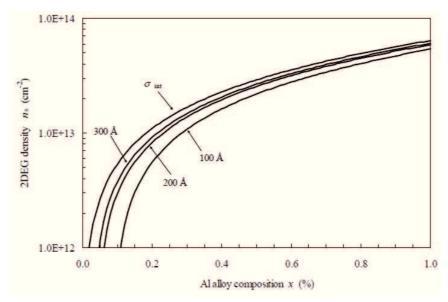

According to the previous equations, the maximum sheet carrier concentration  $n_s$  (x) appearing at the AlGaN/GaN interface can be determined. Clearly, by decreasing the Al concentration of the AlGaN barrier layer, the 2DEG density  $n_s$  decreases. The same behaviour occurs by decreasing the AlGaN thickness barrier layer. From Eq. 2.12 it can be estimated that the formation of the 2DEG is hindered for a critical thickness of the AlGaN barrier layer below 3.5 nm. At same time, it is also important to avoid too thick layer of AlGaN that can lead to relaxation of the structure and, hence, to the suppression of the piezoelectric polarization contribution. In Fig.~2.7 the dependence of the 2DEG sheet carrier concentration  $n_s$  on the Al alloy composition x is shown for different values of the thickness of the AlGaN barrier layer.

Fig. 2.7: Calculated 2DEG density as a function of the Al alloy composition of the  $Al_xGa_{1-x}N$  barrier layer for three different thicknesses. The bound polarization induced sheet charge  $(\sigma_{int})$  is plotted as a reference.

#### 2.4 HEMT working principle

The original idea of the *high electron mobility transistor* (HEMT) based on the presence of a 2DEG, was first introduced for the AlGaAs/GaAs heterostructures and can be attributed to Takashi Mimura in 1979 [83]. The first HEMT fabricated with an AlGaN/GaN heterojunction was demonstrated only in 1991 by another pioneer in this field as M. Asif Khan [35].

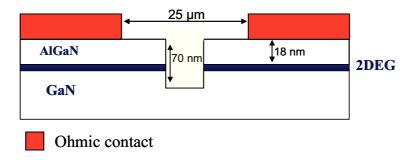

The HEMT is a peculiar device, since it can offer optimal characteristics in terms of both high voltage, high-power and high frequency operation. Its operation principle is founded on the presence of the 2DEG at interface of an heterostructure, like for example an AlGaN/GaN system. It is a three

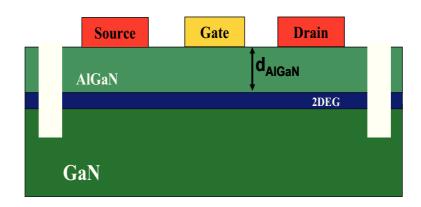

terminal device where the current between the two Ohmic contacts of *source* and *drain*, flowing through the 2DEG, is controlled by the electrode of *gate* (typically a Schottky contact). Practically, the bias applied to the gate controls the flow of electrons through the channel. *Fig. 2.8* shows a schematic of an HEMT device. To confine the electron flow in the 2DEG and isolate HEMT devices, deep trenches (cutting the 2DEG) or ion implantation are typically used.

Fig. 2.8: Schematic of AlGaN/GaN HEMT

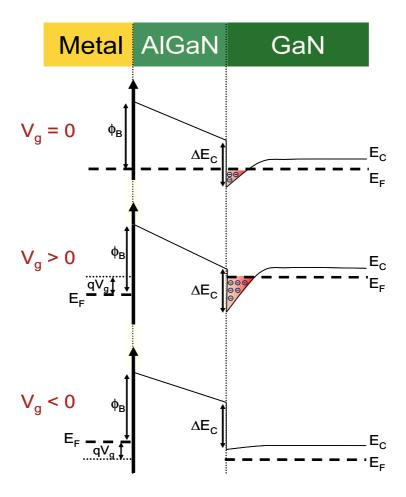

The Fig. 2.9 illustrates, in a schematic band diagram of an AlGaN/GaN HEMT structure, how the 2DEG is influenced by the different gate bias conditions. This schematic is reported for the case of a n-type doped AlGaN barrier layer.

At  $V_g$ = 0 V there are allowed levels below the Fermi level in the subbands of the quantum well, resulting in the presence of a high sheet carrier concentration and in the on-state of the device. By increasing the gate bias ( $V_g > 0$  V), the Fermi level rises, increasing the density of allowed states below the Fermi level in the conductive band, and therefore increasing the sheet carrier concentration of the 2DEG. By decreasing the gate bias  $V_g$  towards negative values ( $V_g < 0$  V) the Fermi level drops depleting the 2DEG, until the position of the Fermi level lies below the quantum well.

Under this condition, the level in the energy subbands are completely empty and the device is in the off-state.

Fig. 2.9: Schematic of the influence of the gate bias on the band diagram (and on the 2DEG) in a n-type doped AlGaN/GaN heterostructure.

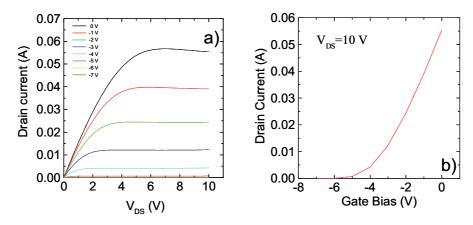

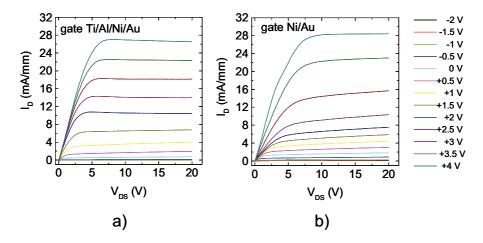

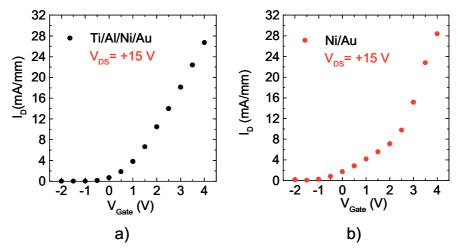

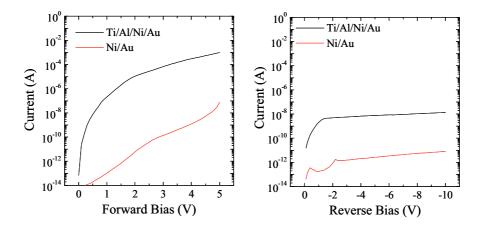

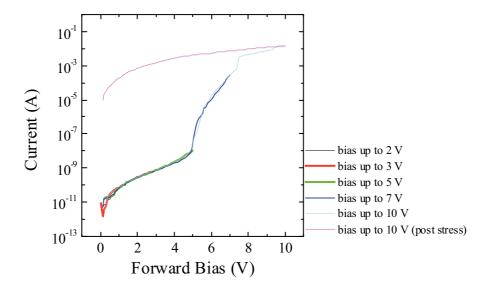

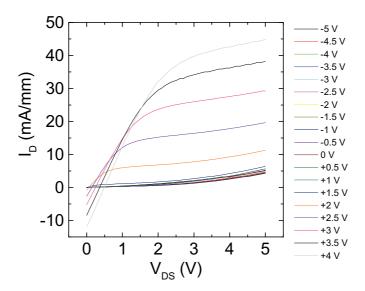

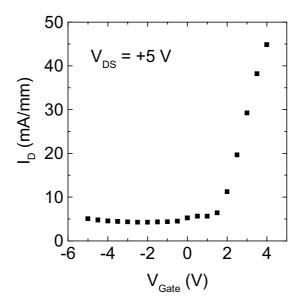

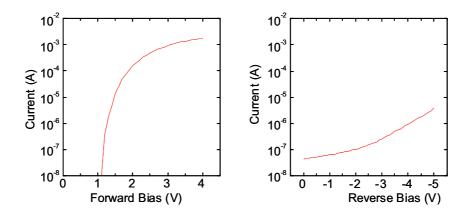

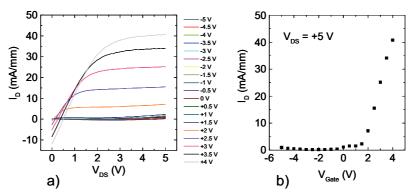

In Fig. 2.10 typical  $I_{DS}$ - $V_{DS}$  characteristics of a HEMT, fabricated during this work of thesis, as a function of the gate bias  $V_g$  (a) and the device transcharacteristic, i.e. the  $I_{DS}$ -Vg at a fixed  $V_{DS}$  (b), are reported as an example.

In the  $I_{DS}$ - $V_{DS}$  characteristics by applying a positive potential difference between source and drain  $(V_{DS})$ , the current will start to flow in the 2DEG. By increasing the drain bias, the current flow in the channel will increase linearly up to certain value. After this value the current through the channel starts to saturate. The maximum saturation value  $I_{DSS}$  depends on the sheet carrier concentration  $n_S$  of the channel. Looking at the transcharacteristics, for a fixed  $V_{DS}$  the drain current  $I_D$  rises with a parabolic behaviour with increasing gate bias.

Fig. 2.10: Example of drain current as function of  $V_{DS}$  for Vg from -7 V to 0 V (a), and drain current as function of gate voltage at  $V_{DS}$ =10 V (b)

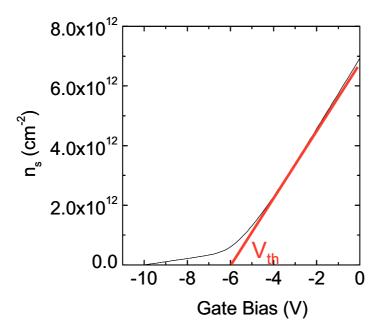

The drain current  $(I_{DS})$  can be controlled by the bias applied to the gate electrode. In particular,  $I_{DS}$  decreases with increasing the negative value of the gate bias  $(V_g)$ , since the region of the channel under the gate is depleted. The value of  $V_g$  which determines the pinch-off of the channel (where the sheet carrier concentration in the channel becomes zero) is called *threshold voltage*  $(V_{th})$  of the device.

In a AlGaN/GaN HEMT at any point x along the channel, neglecting the extrinsic series resistance of source and drain, the sheet carrier concentration depend by the applied  $V_g$

$$n_{S}(x) = \frac{\mathcal{E}_{0}\mathcal{E}_{AlGaN}}{qd_{AlGaN}} \left[ V_{g} - V_{th} - V(x) \right]$$

(Eq. 2.13)

where  $d_{AlGaN}$  is the distance of the gate to the 2DEG channel, corresponding to the AlGaN thickness.

The gate-to-channel capacitance (per unit of area) can be approximately assumed as independent of  $n_s$ , using the expression  $C_{2DEG} = \varepsilon_0 \varepsilon_{AlGaN} / q d_{AlGaN}$ .

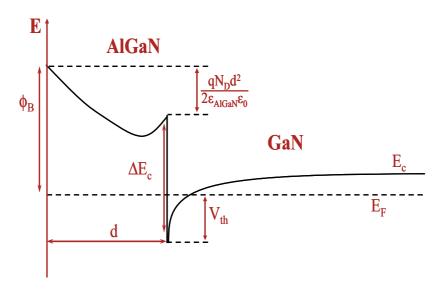

Fig. 2.11: Schematic band diagram for AlGaN/GaN heterostructure, graphically showing the relation between the threshold voltage and other parameters.

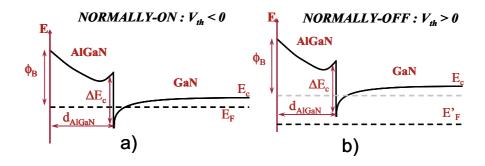

It is now possible to define the *threshold voltage* of the device, as the gate bias necessary to turn-off the 2DEG, resulting in a  $n_S$ =0. Looking at the AlGaN/GaN schematic band diagram showed in *Fig. 2.11*, is clear that the threshold voltage depends on different parameters like the Schottky barrier height  $\phi_B$ , the conduction band offset at the AlGaN/GaN interface  $\Delta Ec$ , the concentration of donor atoms in the AlGaN layer  $N_D$ , the relative dielectric

constant  $\varepsilon_{AlGaN}$ , the thicknesses  $d_{AlGaN}$  and the Al concentration of the AlGaN. Besides these parameters (indicated in Fig. 2.11), in order to have a complete expression of the threshold voltage the contribution of the polarization induced charge density  $\sigma$  must be taken into account. Hence, in a simple form, the threshold voltage can be express as [84]

$$V_{th} = \Phi_B - \Delta E_C - \frac{qN_{D_{AlGaN}}d_{AlGaN}^2}{2\varepsilon_0\varepsilon_{AlGaN}} - \frac{\sigma}{\varepsilon}d_{AlGaN}$$

(Eq. 2.14)

Assuming a constant mobility and remembering the Ohmic law, for a two-dimensional electron gas the conductivity  $\sigma$  of the channel will be directly proportional to the sheet carrier concentration  $n_S$  and to the electrons mobility in the channel  $\mu$

$$\sigma = q \cdot n_{\rm S} \cdot \mu \tag{Eq. 2.15}$$

It is possible to write the drain current as:

$$I_D = -\mu \cdot W \cdot Q(x) \frac{dV(x)}{dx}$$

(Eq. 2.16)

where Q(x) is the charge considered in the channel.

Integrating both sides in the all length of the channel and considering the expression of Q(x) we have

$$I_{D} = \mu \cdot \frac{W}{I} \cdot C_{2DEG} \int_{V_{c}}^{V_{D}} \left[ V_{g} - V_{th} - V(x) dV(x) \right]$$

(Eq. 2.17)

The drain current of a HEMT in linear region is often expressed in a form similar to that used for a MOSFET, i.e., :

$$I_D = \mu \cdot \frac{W}{L} \cdot C_{2DEG} \left( V_g - V_{th} - \frac{V_{DS}}{2} \right) V_{DS}$$

(Eq. 2.18)

Increasing  $V_{DS}$  up to certain value called  $V_{DSsat}$ , the drain current  $I_D$  start to saturate. In this region the  $I_D$  is constant and so the derivate of  $I_D$  will be zero.

$$\frac{dI_{D}}{dV_{DS}} = \mu \cdot q \frac{W}{L} C_{2DEG} (V_g - V_{th} - V_{DS}) = 0$$

(Eq. 2.19)

and V<sub>DSsat</sub> is given by

$$V_{DSsat} = V_g - V_{th} \tag{Eq. 2.20}$$

At bias condition of V<sub>DSsat</sub> the I<sub>D</sub> will be express as

$$I_{DSS} = \frac{1}{2} \mu \cdot \frac{W}{L} \cdot C_{2DEG} (V_g - V_{th})^2$$

(Eq. 2.21)

that represent the drain current in saturation region.

Eq. 2.21 is an approximation valid for long channel devices. However, for HEMTs with a short gate length ( $l_g < 10~\mu m$ ), the electron transport occurs under high electric fields and the expression of the saturation current is different. If the electric fields exceeds a certain critical value, the speed of the electrons in the 2DEG begins to saturate. Taking into account the effects of the saturation velocity model [85] the saturation current is expressed as

$$I_{DSS} = q \cdot n_S \cdot v_{sat}$$

(Eq. 2.22)

Considering the expression of the drain current, it is also possible to define the transconductance of the device as the change in drain current  $I_D$  resulting from a variation of gate voltage  $V_g$  for a fixed  $V_{DS}$ :

$$g_m = \frac{\partial I_D}{\partial V_g}\Big|_{V_{\text{re}} = const}$$

(Eq. 2.23)

Similarly the output conductance of the device is defined as the  $I_D$  response to a  $V_{DS}$  variation for a fixed gate bias  $V_g$

$$g_d = \frac{\partial I_D}{\partial V_{DS}}\Big|_{V_{-}=const}$$

(Eq. 2.24)

## 2.5 Determination of the 2DEG properties from the HEMT characteristics

According to the description given in the previous section, it is clear that the characteristics of HEMT devices depend strongly on the properties of the 2DEG, namely on the carrier concentration and mobility of the electrons in the channel.

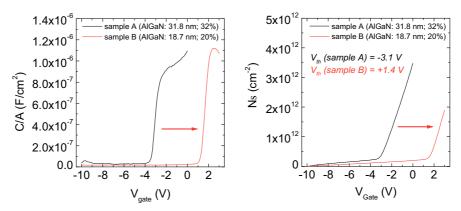

This paragraph describes how it is possible to determine the relevant properties of the 2DEG, reporting some examples of experimental data acquired on test-devices fabricated during the work of this thesis.

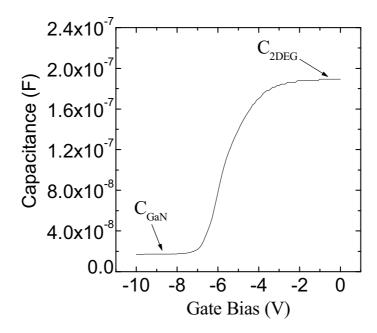

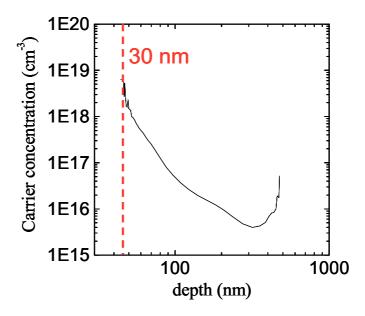

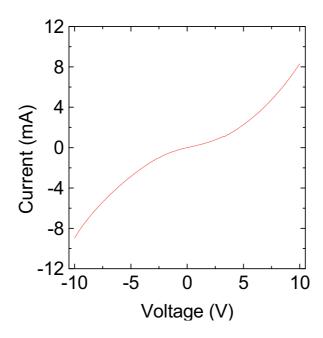

A common way to study the 2DEG properties is the combined analysis of the current voltage (I-V) and capacitance voltage (C-V) measurements on HEMT test structures.

In particular, by C-V measurements performed on the gate-source diode it is possible obtain important information, such as the sheet carrier concentration  $n_S$ , the carrier density profile as a function of the depth, and the distance d of the 2DEG from the AlGaN surface. Furthermore, from the I-V characteristics of the devices it is possible to determine the channel conductance. Combining the information obtained by C-V and I-V measurements, the electron mobility in the channel  $\mu_{2DEG}$  can be extracted.

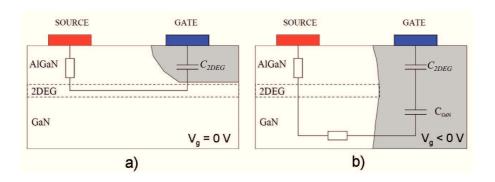

A schematic of the variation of the depletion region with the applied gate bias is shown in *Fig. 2.12*. Considering a Schottky diode with a contact area A formed onto a heterostructure with a uniform 2DEG concentration, under

an applied reverse bias  $V_{\text{R}}$  the width of the depletion region under the contact is

$$w = \sqrt{\frac{2\varepsilon_0 \varepsilon_{AlGaN}}{qN} (V_{bi} - V_R)}$$

(Eq. 2.25)

where  $V_{bi}$  is the intrinsic potential difference at gate voltage zero and  $V_R$  is the reverse bias applied to the Schottky gate contact.

For a HEMT with a Schottky gate contact biased at  $V_g$ =0 V, the capacitance normalized by the Schottky contact area A of the depletion region is express as

$$C_{V_g=0} = \frac{dQ}{dV}\Big|_{V_g=0} = \frac{\mathcal{E}_0 \mathcal{E}_{AlGaN}}{w}$$

(Eq. 2.26)

where w in this case extends up to the 2DEG and corresponds to the distance d of the 2DEG from the AlGaN surface (see Fig. 2.12a).

By applying a negative bias to the gate contact (*Fig. 2.12b*), the depletion region under the contact starts to expand, depleting the 2DEG and extending inside the intrinsic GaN buffer layer.

Fig. 2.12: Schematic of the depletion region at  $V_g$ =0 V (a) and in case of  $V_g$ <0 V (b). Figure is taken from [86].

When the channel is completely depleted, the capacitance of the depletion region will be given by the contributions of two capacitances in series, the capacitance due to the 2DEG and the capacitance due to the intrinsic layer of GaN. Because of its intrinsic state and its significantly larger thickness, the GaN layer contributes to the total capacitance with a smaller capacitance  $C_{GaN} < C_{2DEG}$ , that in case of two capacitance in series become dominant.

$$\frac{1}{C_{tot}} = \frac{1}{C_{2DFG}} + \frac{1}{C_{GaN}}$$

(Eq. 2.27)

The *Fig. 2.13* shows an example of a C-V measurement acquired on a HEMT structure in the gate bias range from -10 V to 0 V.

Fig. 2.13: Capacitance of a HEMT as function of gate voltage

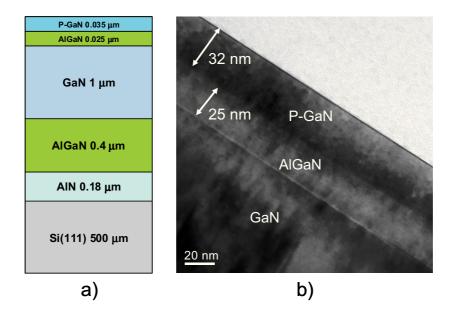

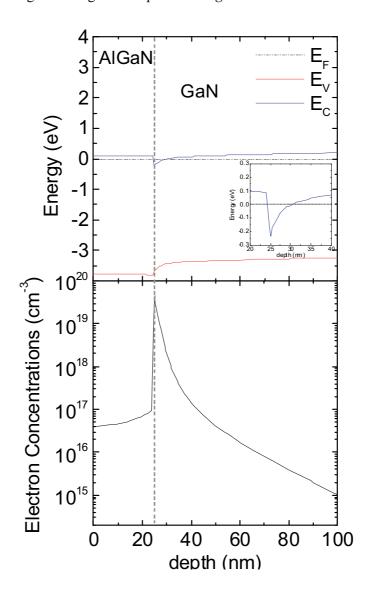

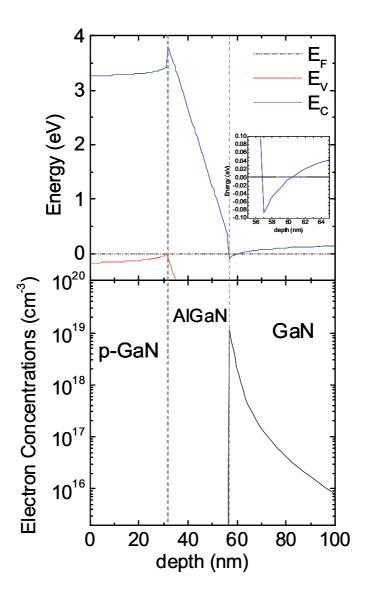

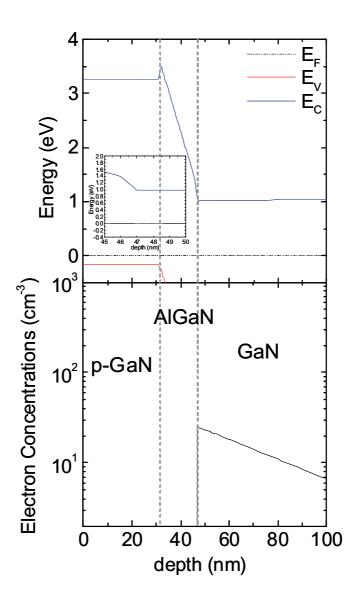

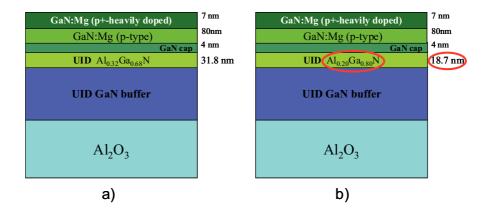

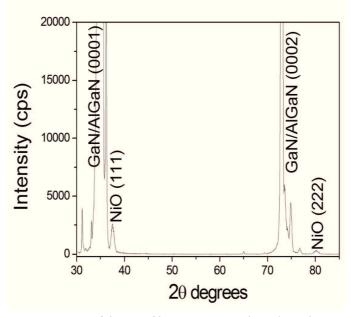

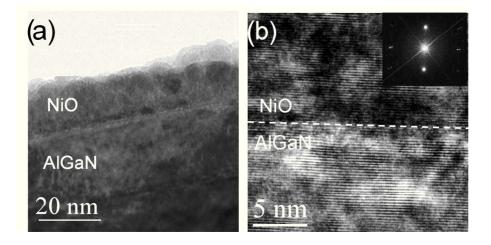

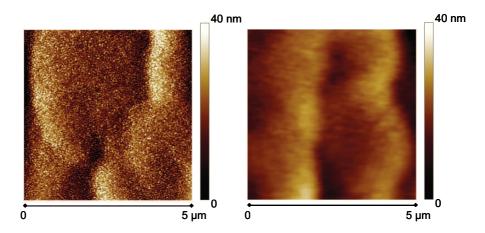

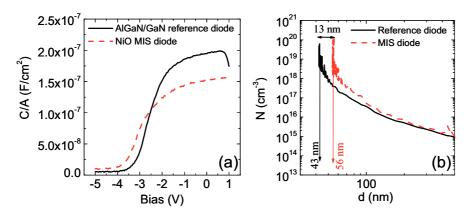

By combining Eq. 2.25 and Eq. 2.26 it is possible obtain the capacitance for a depletion region w